Belgrade, June 23rd, 2022

Minimize the effects of technological process imperfections, provide the required circuit functionality, and fulfil the factory criteria, so that the integrated circuit can be manufactured. Sounds good? Let’s learn more about IC Layout engineering!

Milos Lazic, Analog IC Layout Engineer at Elsys Eastern Europe, will introduce you to IC Layout engineering and the way you can start your career in this area of expertise. Milos will emphasize the scale of impact and responsibilities IC Layout engineering has on the process of silicon chip development and what it takes to be successful.

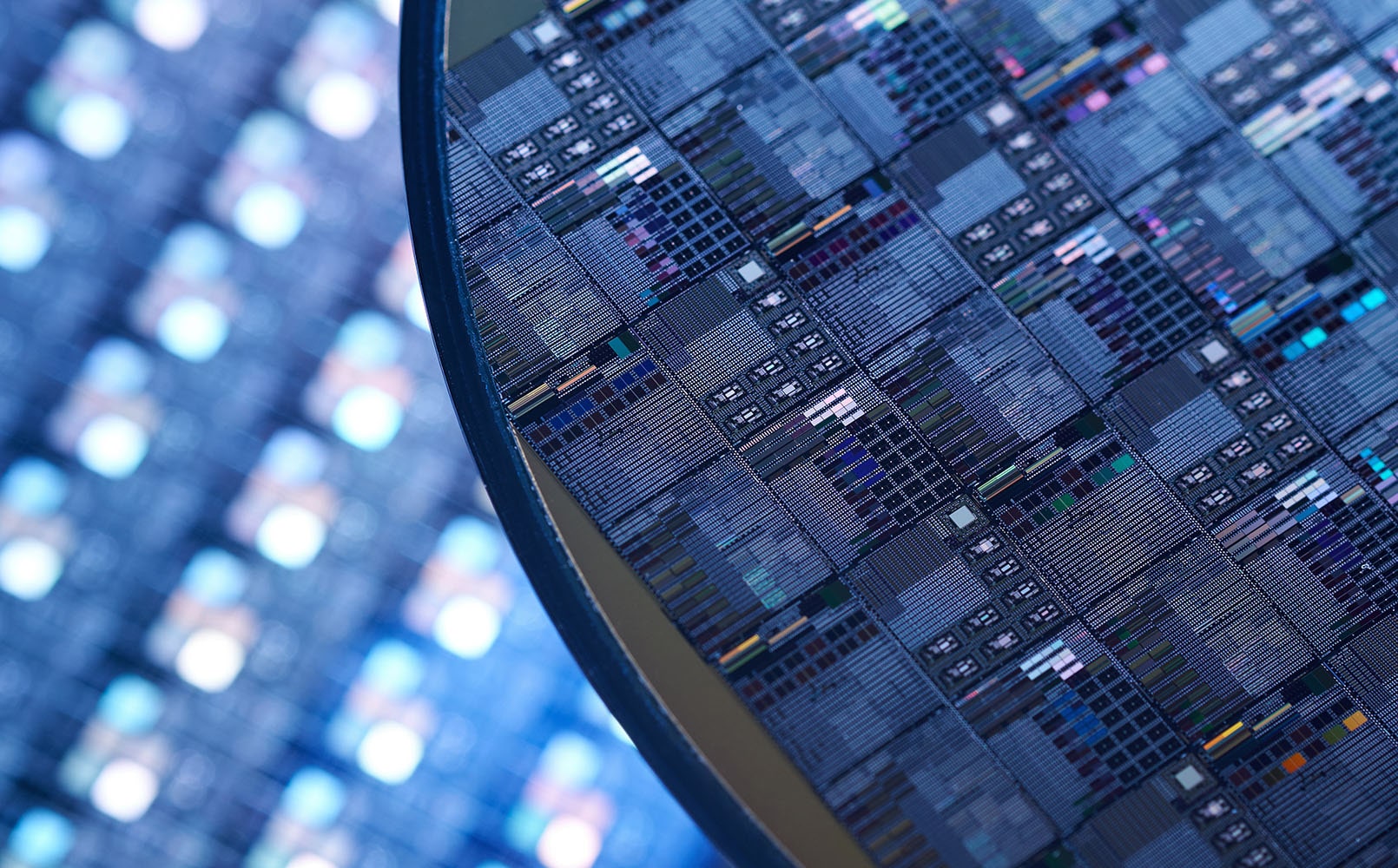

“Elsys Eastern Europe has been successfully designing integrated circuit layouts for 15 years. During this period, the engineers had the opportunity to work on the development of several dozen integrated circuits in various technologies from robust to state-of-the-art such as 7 nanometer FinFET technologies.”

We’ve put huge effort in creating a such an internship program that will easily open a path towards becoming and IC Layout engineer. First of all, we must emphasise that IC Layout is a very challenging and an exciting career path. Because you’ll have the opportunity to work on multiple projects that will enhance your engineering capabilities, encourage creativity and out-of-the-box thinking.

You’re probably thinking how this position is going to inspire me to be more creative. Well, here’s a fun fact. Did you know that an IC Layout engineer can add his personal signature on every silicon chip he designed? With this said, the layout of analog circuits is designed with Full custom methodology where a layout engineer has absolute control over the positions of each component on the chip and each connection.

“The internship program has three modules lasting three months in total. During this period, candidates go through theoretical lectures and practical exercises.”

When it comes to theoretical lecturing segment of the internships, our interns will have a chance to work with our best engineers who continuously try to facilitate the learning process and pass their knowledge to our interns. During the practical teaching segment, our interns can work on the most modern equipment and licensed software that are the standard in the development of integrated circuits. Practice is performed on the real analog circuits that are developed for the needs of commercial projects in our company.

If you’ve enjoyed reading this article, then look no further. Elsys Eastern Europe is the place for you.

Check out our open IC Layout internship and apply!

WHERE PASSION LEADS TO EXCELLENCE